ZYBOで遊ぶ02:AXI CDMA IPを使ってみた(1)

ZYBOで遊んだメモ

ZYBOで遊ぶ02:AXI CDMA IPを使ってみた(1) - ThuruThuruToru’s blog

ZYBOで遊ぶ02:AXI CDMA IPを使ってみた(2) - ThuruThuruToru’s blog

やったこと

AXI CDMA IP(AXI4 <-> AXI4) を使ってみたのでメモ書き.

今回はRTLはいじらず,PS部にAXI CDMA IPをつないだだけのシステムを作り,

Xilinx SDKでDMACを操作するSWを書いて DRAM<->DRAM のデータ転送をしてみた.

1. VivadoでHWデザイン作成

1.1. ZYNQ7 Processing Systemの追加

Vivadoのプロジェクトを作成した後,Generate Block Design をクリックし,Add IP で ZYNQ7 Processing Systemをダブルクリック.

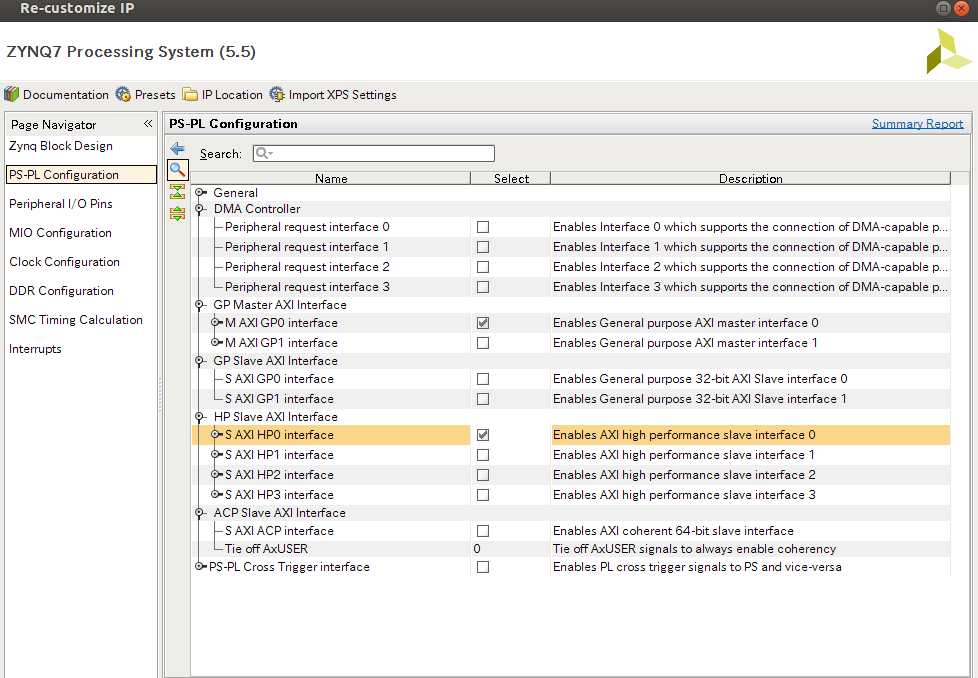

作成された ZYNQ7 Processing System をダブルクリックして以下の設定を行う.

- Import XPS Settings で ZYBO_zynq_def.xml を指定(いつもと同じ)

- PS-PL Configuration で S AXI HP0 interface を選択する

- このSlaveポートにAXI CDMAがマスタとしてつながる

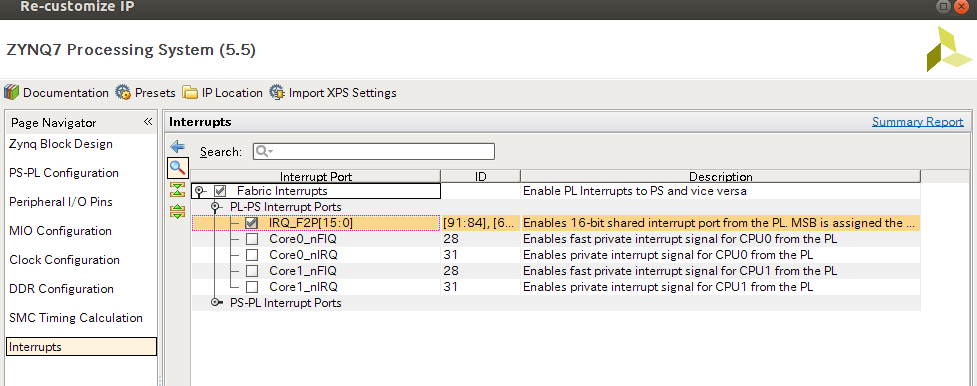

- Interrupts で IRQ_F2P を選択する

- AXI CDMAの割り込み用

1.2. AXI CDMAの追加

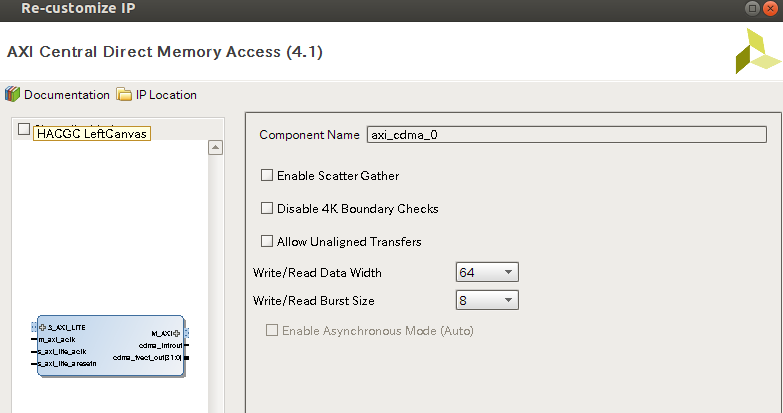

Add IP でAXI Central Direct Memory Accessをダブルクリック.

作成された AXI Central Direct Memory Access をダブルクリックして以下の設定を行う.

- Enable Scatter Gather のチェックを外す

- 外さなくてもいいが,今回はScatter Gatherを使わない

- Write/Read Data Width を 64にする

- S AXI HP0 はデータが64bit幅なので効率良く転送できるように合わせる

1.3. IPをつなぐ

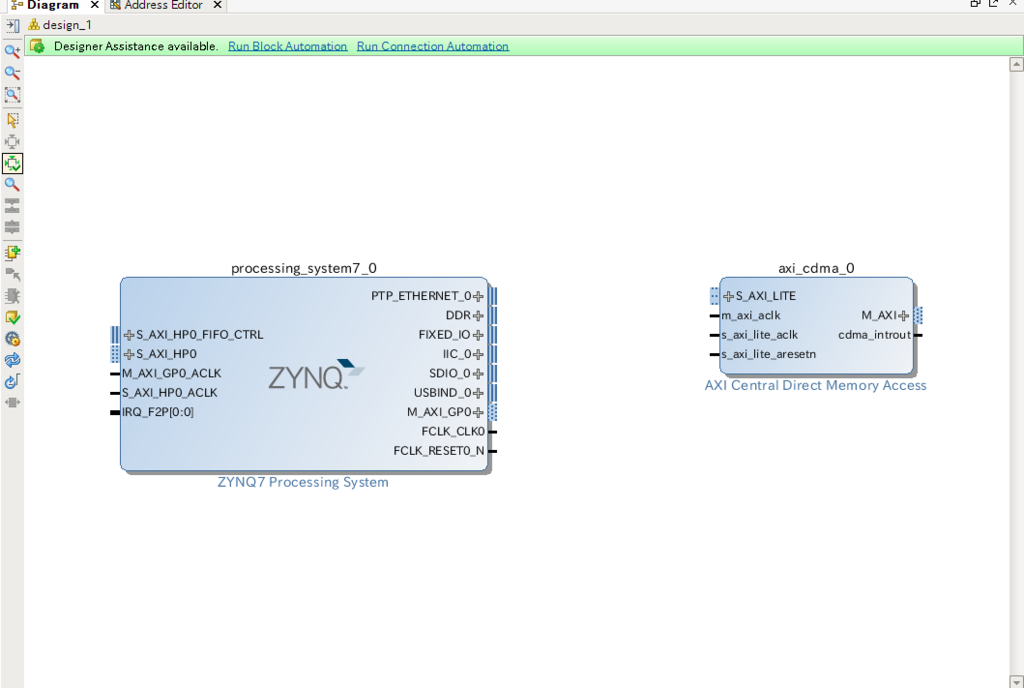

Processor System と AXI CDMA をつなぐ.

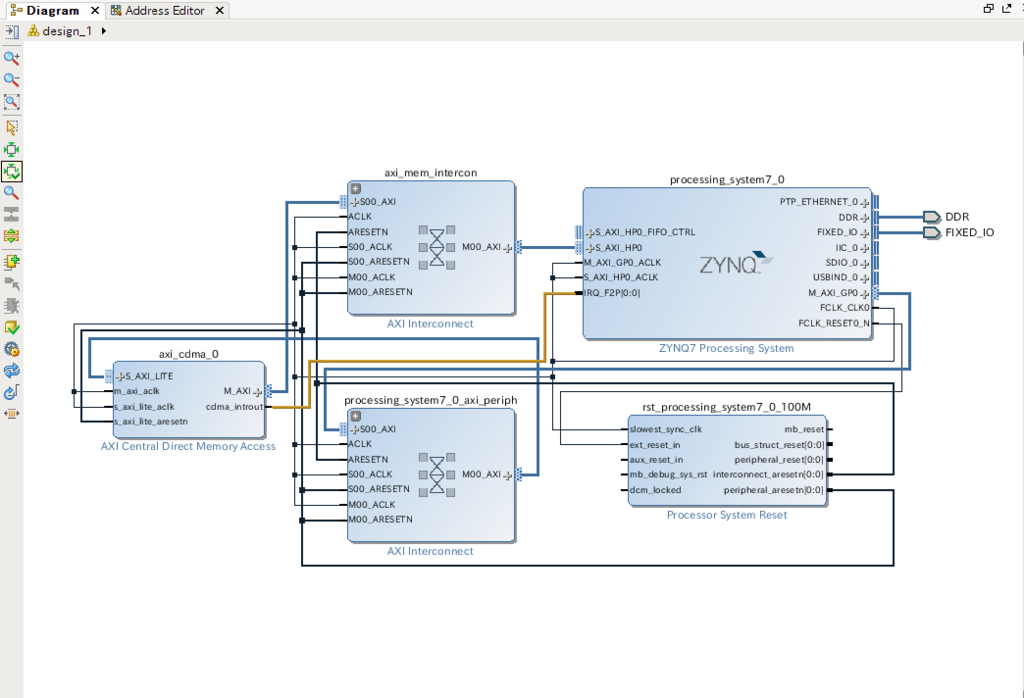

ここまでで上の図のようになっているので,上部に表示されている「Run Block Automation」と「Run Connection Automation」を実行する.

割り込み信号は自動でつながらないので,Processing System の IRQ_F2P と AXI CDMA の cdma_introut をマウスでつなぐ.

Validate Designを実行し,デザインに問題がないことを確認.

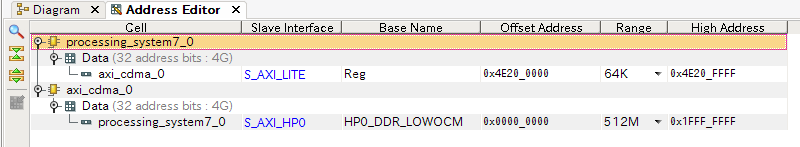

アドレスエディタを開いてみると,自動で以下の様に割り当てられていた.問題ないのでいじらない.

1.4. Bitstream 作成

Sourcesタブ内のdesign_1(自分でつけたBlock Design名)を右クリックし,Create HDL Wrapperを指定し,Topモジュールを自動生成する.

Project Manager->Program and Debug->Generate Bitstreamをクリックし,Bitstream作成.

File->Export->Export Hardwareをクリックし,Include bitstreamにチェックを入れてOKボタンを押す.

File->Launch SDKをクリックして,Xilinx SDK(Eclipse)を立ち上げる.

VivadoでのHWデザインの作成は完了.ここからはXilinx SDKでSWを書いていく.

ZYBOで遊ぶ02:AXI CDMA IPを使ってみた(2) - ThuruThuruToru’s blog に続く